## IoT に向けた低消費電力周波数シンセサイザ設計

## Energy-efficient Frequency Synthesizer Design for IoT

岡田 健一 Kenichi OKADA

東京工業大学

## 概要

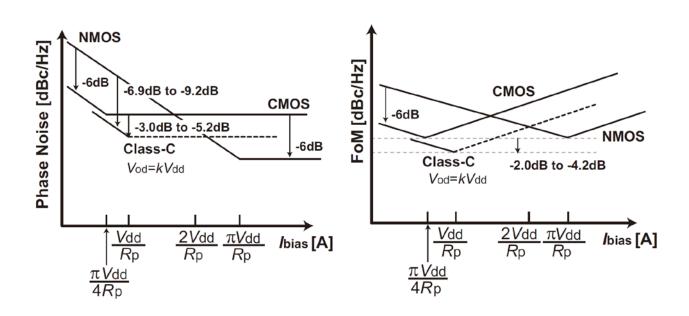

本基礎講座では、IoT 用バッテリーレス無線機の実現に向けた極低消費電力発振器の構成方法について解説する。まずは、LC 共振器の基本原理について解説し、位相雑音と消費電力のトレードオフを示す指標である FoM について詳説する。発振器のトポロジーごとにこれらの性能は決まり、所望の位相雑音レベルにより、適切に選択する必要がある。本講演では、NMOS, PMOS, CMOS (push-pull)、tailfiltering、Class-C、Class-D、Class-F、clip&restore、pulse-driven型のLC発振器について解説する。また、近年のPLL (AD-PLL、SS-PLL、DTC+PLL、IL-PLL)についても簡単に紹介する。

## Abstract

In this seminar, a ultra-low-power (ULP) frequency synthesizer design for a battery-less IoT transceiver is explained. Firstly, a theoretical basics of LC VCO (Voltage-Controlled Oscillator) is discussed especially about the trade-off between phase noise and power consumption, which can be indicated by FoM. The limit of FoM is determined by VCO topology and LC-tank quality factor. Variants of VCO such as NMOS, PMOS, CMOS (push-pull), tail-filtering, Class-C, Class-D, Class-F, clip&restore, pulse-driven, etc will be explained. Finally, recent PLL variants will also be introduced briefly.

図2:回路構成とFoM

図1:位相雑音と消費電力