# Sパラメータと高周波増幅器の基礎

Foundation of S-Parameter and Silicon High-Frequency Amplifier

藤本 竜一

Ryuichi Fujimoto

(株) 東芝 セミコンダクター社

Toshiba Corp. Semiconductor Company

〒 247-8585 横浜市栄区笠間 2-5-1

2-5-1, Kasama, Sakae-Ku, Yokohama 247-8585, Japan

e-mail: ryuichi.fujimoto@toshiba.co.jp

## Abstract

Foundation for design of a low-noise amplifier (LNA) is explained in this paper. Firstly, S-parameter and Smith chart which are basic tools to design LNAs, are explained. After that, a basic design procedure for a LNA is described. Finally, actual design examples of LNAs using by Si-BiCMOS and CMOS process are presented.

## 1 はじめに

十数年前までは、高周波回路は化合物半導体を用いて製造されてきた。しかし、携帯電話や無線 LANなどの高周波回路を用いた民生機器が広く普及するにつれ、これらの機器に用いる高周波回路も安価で、量産性に優れた BiCMOS や CMOS などの Si プロセスで実現されるようになってきた。本講座では、高周波回路を設計するために必要となる S パラメータやスマスチャートなどの基礎知識と低雑音増幅器 (LNA) を例に高周波回路の設計手法と実際の設計事例について紹介する。

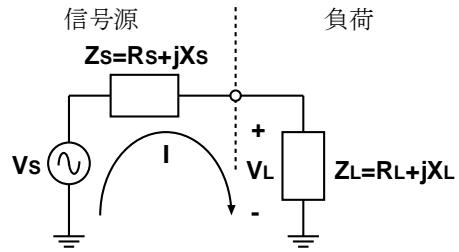

図 1: 信号源から負荷へ供給し得る電力

ピーダンス  $Z_L$  にかかる電圧  $V_L$  は、

$$I = \frac{V_S}{Z_S + Z_L} \quad (1)$$

$$V_L = IZ_L \quad (2)$$

## 2 LNA 設計のための基礎知識

### 2.1 インピーダンス整合

インピーダンス整合を理解するために、図 1 に示すような信号源インピーダンス  $Z_S$  の信号源からインピーダンス  $Z_L$  の負荷に供給し得る最大の電力をについて考える。この回路に流れる電流  $I$  と負荷イン

であるため、負荷インピーダンス  $Z_L$  に供給される電力は、

$$\begin{aligned} P_L &= \Re\{V_L I^*\} \\ &= \frac{R_L |V_S|^2}{(R_S + R_L)^2 + (X_S + X_L)^2} \end{aligned} \quad (3)$$

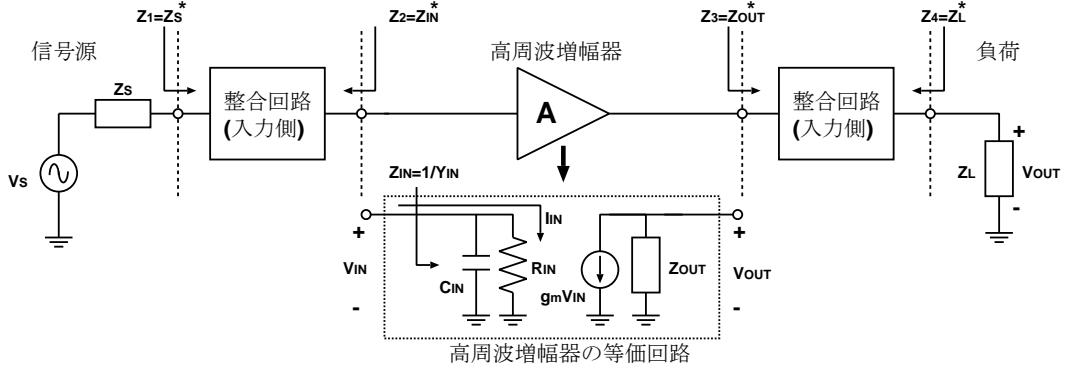

図 2: 高周波増幅器のインピーダンス整合

となり、ある信号源インピーダンス  $Z_S = R_S + jX_S$  が決まると、

$$Z_L = Z_S^* \quad (4)$$

の負荷を接続すると信号源から負荷に供給される電力は最大となり、そのときの電力  $P_{MAX}$ (最大有能電力)は

$$P_{MAX} = \frac{|V_S|^2}{4\Re\{Z_S\}} \quad (5)$$

となる。このように式 (4) が成り立ち、信号源から最大の電力を引き出している状況をインピーダンス整合と言う。

図 2 に示す高周波増幅器におけるインピーダンス整合について考える。一般的に、信号源インピーダンス  $Z_S$  と増幅器の入力インピーダンス  $Z_{IN}$  は式 (4) に示したような複素共役の関係にはなく、同様に増幅器の出力インピーダンス  $Z_{OUT}$  と負荷インピーダンス  $Z_L$  も式 (4) に示したような複素共役の関係にはない。このためインピーダンス整合を実現するためには、図 2 に示すように、増幅器の入力側と出力側にインピーダンス整合回路 (Impedance Matching Circuit) が必要となる。整合回路は、一般的には電力を消費しないインダクタとキャパシタなどの受動素子を用いて構成される。図 2 の増幅器の入力側から、入力側の整合回路を介して信号源を見たインピーダンスが  $Z_2 = Z_{IN}^*$  となるような整合回路を用いて、インピーダンス整合を実現する。なお、インピーダンス整合が実現している場合、信号源側から整合回路を介して見た増幅器の入力インピーダンスに関しては、 $Z_1 = Z_S^*$  同時にが成り立っている。

整合回路を用いてインピーダンス整合が成り立っている場合、増幅器の入力インピーダンス  $Z_{IN}$  には式 (5) の最大有能電力が供給されることとなる。こ

の最大有能電力は増幅器の入力インピーダンスの実部  $R_{IN}$  で消費されるため、 $R_{IN}$  に流れる電流は

$$|I_{IN}| = \sqrt{\frac{P_{MAX}}{R_{IN}}} = \frac{|V_S|}{\sqrt{4R_S R_{IN}}} \quad (6)$$

となり、増幅器の入力にかかる電圧は

$$|V_{IN}| = \frac{|V_S|}{\sqrt{4R_S R_{IN}}} |R_{IN}| = \sqrt{\frac{R_{IN}}{4R_S}} |V_S| \quad (7)$$

となり、 $R_{IN} > 4R_S$  である場合、増幅器の入力には元々の信号源の電圧である  $V_S$  よりも大きな電圧がかかる [3]。

## 2.2 S パラメータ

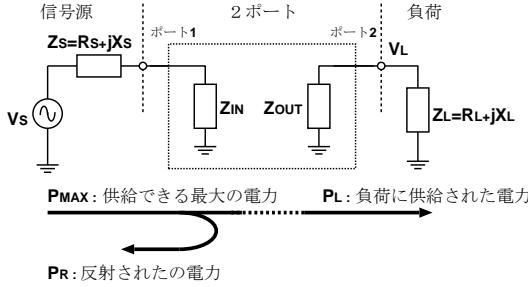

図 3 に示すインピーダンス整合の条件が成り立っていない一般的な 2 ポートに関して考える [1, 3]。この場合 2 ポートの入力インピーダンス  $Z_{IN}$  に供給される電力は

$$P_{IN} = \Re\left\{ \frac{Z_{IN}}{|Z_S + Z_{IN}|^2} \right\} |V_S|^2 \quad (8)$$

となる。ここで、信号源から取り出し得る電力  $P_{MAX}$  と実際に 2 ポートの入力に供給された電力の差を

$$P_R = P_{MAX} - P_{IN} = \frac{Z_{IN} - Z_S^*}{Z_{IN} + Z_S} |V_S|^2 P_{MAX} \quad (9)$$

と定義し、この分の電力は信号源とポート 1 のインピーダンスの不整合によって、信号源側に反射されたと考える。また、負荷側に供給される電力は、

$$P_L = \frac{\Re\{Z_L\}}{|Z_L|^2} |V_L|^2 \quad (10)$$

となる。

図3: インピーダンス整合していない2ポートへの電力の供給

ここで、電力は電圧と電流の積で定まる量であり、線形回路において電圧や電流で成り立つ重ね合わせの理を用いることができない。このため、電力を直接扱うかわりに、図3および図4のポート1側の入射量  $a_1$ 、反射量  $b_1$ 、透過量  $b_2$  を以下のように定義する。

$$a_1 a_1^* = P_{MAX} = \frac{V_{in}}{4\Re\{Z_{in}\}} = \frac{V_S V_S^*}{4\rho_1 \rho_1^*} \quad (11)$$

$$\begin{aligned} b_1 b_1^* &= P_R = \left| \frac{Z_{in} - Z_S^*}{Z_{in} + Z_S} \right|^2 \frac{V_{in}}{4\Re\{Z_{in}\}} \\ &= \frac{Z_{in} - Z_S^*}{Z_{in} + Z_S} \left( \frac{Z_{in} - Z_S^*}{Z_{in} + Z_S} \right)^* \frac{V_S V_S^*}{4\rho_1 \rho_1^*} \end{aligned} \quad (12)$$

$$b_2 b_2^* = P_L = \frac{\Re\{Z_L\} |V_L|^2}{|Z_L|^2} = \frac{\rho_2 \rho_2^* V_L V_L^*}{Z_L Z_L^*} \quad (13)$$

ここで  $\rho_1$  および  $\rho_1^*$  は

$$\rho_1 \rho_1^* = \Re\{Z_S\}, \quad \rho_2 \rho_2^* = \Re\{Z_L\} \quad (14)$$

であり、以上より

$$a_1 = \frac{V_{in}}{2\rho_1} \quad (15)$$

$$b_1 = \frac{Z_{in} - Z_S^*}{Z_{in} + Z_S} \frac{V_0}{2\rho_1} \quad (16)$$

$$b_2 = \rho_2 \frac{V_2}{Z_2} \quad (17)$$

となる。

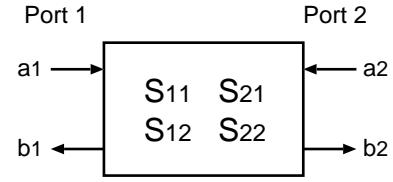

ここでは図3のポート1から信号が入力した場合について計算したが、ポート2から信号が入力した場合についても全く同様に計算ができ、重ね合わせの理が成り立つ量である  $a_1, a_2, b_1, b_2$  を用いて2ポートのSパラメータを

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix} \quad (18)$$

図4: Sパラメータの定義

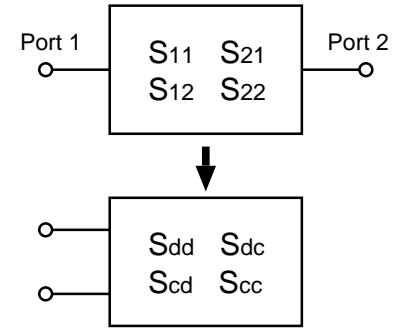

図5: Sパラメータの差動表現

と定義する。  $S_{11}$ 、  $S_{21}$  は

$$S_{11} = \frac{b_1}{a_1}|_{a_2=0} = \frac{Z_{in} - Z_S^*}{Z_{in} + Z_S} \quad (19)$$

$$S_{21} = \frac{b_2}{a_1}|_{a_2=0} = \frac{2\rho_1 \rho_2 V_2}{V_{in} Z_L} \quad (20)$$

となり、  $S_{11}$  はポート2からの入力電力が0( $a_2 = 0$ )の場合の入射電力  $a_1$  と反射電力  $b_1$  の比であり、  $S_{21}$  はポート2からの入力電力が0の場合の入射電力  $a_1$  と透過電力  $b_2$  の比である。 $S_{12}$  及び  $S_{22}$  に関しては2ポートの入力と出力を反対に接続して考えれば、全く同様に計算することができる。

次に図5に示すようなSパラメータの差動表現について考える。図5に示すような2ポートのSパラメータを差動のSパラメータに変換するには、以下の式を用いる [5]。

$$\begin{bmatrix} b_{dm} \\ b_{cm} \end{bmatrix} = \begin{bmatrix} S_{dd} & S_{dc} \\ S_{cd} & S_{cc} \end{bmatrix} \begin{bmatrix} a_{dm} \\ a_{cm} \end{bmatrix} \quad (21)$$

ここで、

$$S_{dd} = \frac{S_{11} - S_{21} - S_{12} + S_{22}}{2} \quad (22)$$

図 6: インピーダンス平面からスミスチャートへの変換

$$S_{dc} = \frac{S_{11} - S_{21} + S_{12} - S_{22}}{2} \quad (23)$$

$$S_{cd} = \frac{S_{11} + S_{21} - S_{12} - S_{22}}{2} \quad (24)$$

$$S_{cc} = \frac{S_{11} + S_{21} + S_{12} + S_{22}}{2} \quad (25)$$

であり、 $S_{dd}$  は差動の反射係数を、 $S_{cc}$  は同相の反射係数を表す。

### 2.3 スミスチャート

図 3 に示すような 2 ポート回路において、一般的には信号源インピーダンス  $Z_S$  と負荷インピーダンス  $Z_L$  は等しく

$$Z_S = Z_L = Z_0 \quad (26)$$

となっており、この  $Z_0$  を特性インピーダンスと言う。通常は  $Z_0 = 50\Omega$  となっている場合が多く、このような系を  $50\Omega$  系と言う。式 (19) より  $S_{11}$  はポート 1 における入射量  $a_1$  と反射量  $b_1$  の比になっているため反射係数とも呼ばれ、式 (19) より

$$\Gamma_1 = S_{11} = \frac{Z_{IN} - Z_0^*}{Z_{IN} + Z_0} \quad (27)$$

と書ける。一般的な  $50\Omega$  系で考えると、式 (27) は

$$\Gamma_1 = S_{11} = \frac{Z_{IN} - 50}{Z_{IN} + 50} = \frac{Z_{IN}/50 - 1}{Z_{IN}/50 + 1} = \frac{z_{IN} - 50}{z_{IN} + 50} \quad (28)$$

となる。ここで、 $z_{IN} = Z_{IN}/50$  は特性インピーダンスである  $50\Omega$  で規格化したインピーダンスである。 $Z_{IN} = 50\Omega$  でインピーダンス整合が成立する場合は  $S_{11} = 0$  となり入力された電力は全て負荷に供給され

(無反射)、 $Z_{IN} = 0$ (ショート) の場合は  $S_{11} = -1$ 、 $|Z_{IN}| \rightarrow \infty$ (オープン) の場合は  $S_{11} = 1$  となり、どちらの場合も入力された電力は負荷に全く供給されない(全反射)。このように、 $S_{11}$  は入力インピーダンス  $Z_{IN}$  から一意に決まるため、入力インピーダンスと等価な量であると考えられる。

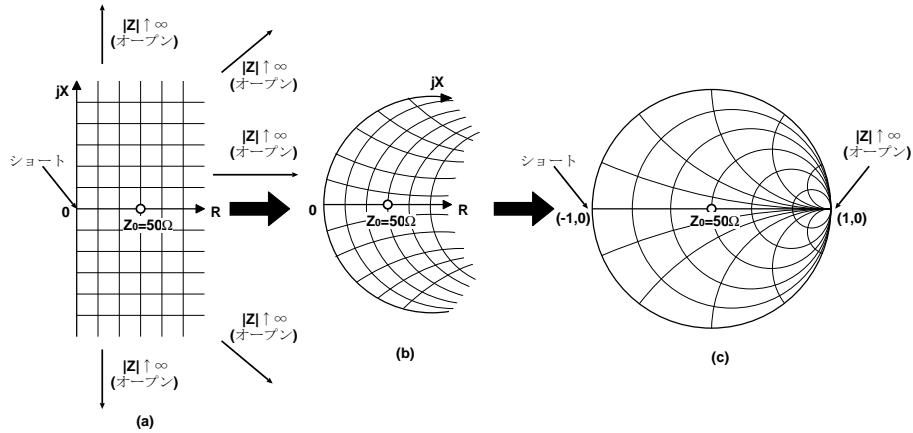

式 (28) は規格化されたインピーダンス  $Z_{IN}/50$  を  $S_{11}$ (または反射係数  $\Gamma_1$ ) に変換する写像であるが、この写像を模式的に示したものが図 6 である [2, 3]。図 6(a) は、X 軸に実軸をとり、Y 軸に虚軸をとったインピーダンス平面を表している。一般的にはインピーダンスの実部は正であるので、図 6(a) では実軸の正の部分のみを考える。式 (28) で表される写像は図 6 に示すように、インピーダンス平面の虚軸を単位円上に、 $|Z_{IN}| \rightarrow \infty$  の点(オープン)を単位円の(1,0)の座標に、 $Z_{IN} = 0$  の点(ショート)を単位円の(-1,0)の座標に変換する写像である。図 6(c) が変換後の図で、スミスチャートと言う。

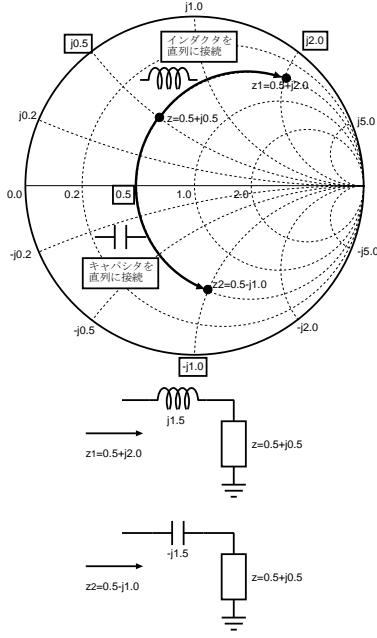

一般にスミスチャートと言った場合、図 6(c) や図 7 に示すようなインピーダンスチャートを言うことが多いが、図 8 に示すアドミタンスチャートも用いられる。ここで例として、 $Z = 25 + j25$  の場合を図 7 のスミスチャート上にプロットする。与えられたインピーダンス  $Z$  を特性インピーダンスである  $Z_0 = 50\Omega$  で規格化すると  $z = Z/Z_0 = 0.5 + j0.5$  となる。この  $z$  をスミスチャート上の目盛に沿ってプロットすると、図 7 に示す位置になる。 $z$  に直列にインダクタやキャパシタを接続すると、インピーダンスは図 7 に示すようにスミスチャート上を移動する。例えば  $j\omega L = j75$  となるようなインダクタ  $L$  が  $Z$  に直列に接続されたとすると、 $j\omega L$  を特性インピーダンス

図 7: インピーダンスチャート

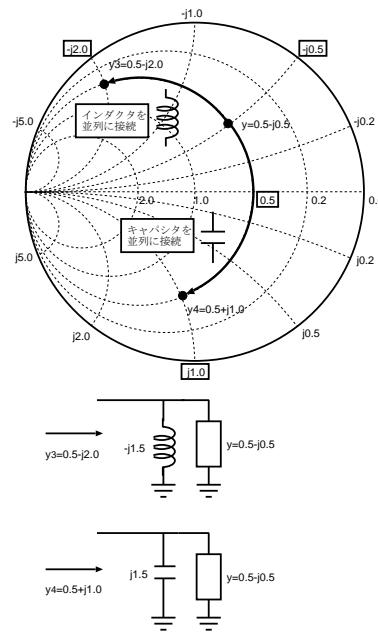

図 8: アドミタンスチャート

$Z_0$  で規格化した  $j1.5$  だけスミスチャート上を移動する。同様に、 $1/(j\omega C) = -j75$  となるようなキャパシタ  $C$  が  $Z$  に直列に接続されたとすると、特性インピーダンス  $Z_0$  で規格化した  $-j1.5$  だけスミスチャート上を移動する。

アドミタンスチャートに関して同様で、 $Y = 0.01 + j0.01$  の場合を図 8 に示す。特性アドミタンス  $Y_0 = 1/Z_0$  で規格化したアドミタンス  $y$  は  $y = Y/Y_0 = Z_0 Y = 0.5 + j0.5$  となり、例えば  $j\omega C = j0.03$  となるようなキャパシタ  $C$  が  $Y$  に並列に接続されたとすると、 $j\omega C$  を規格化した  $j\omega C/Y_0 = j1.5$  だけスミスチャート上を移動する。同様に、 $1/(j\omega L) = -j0.03$  となるようなインダクタ  $L$  が  $Y$  に並列に接続されたとすると、規格化した  $-j1.5$  だけアドミタンスチャート上を移動する。

以上より、適当な素子値のインダクタやキャパシタを直列または並列に接続することにより、与えられたインピーダンスをスミスチャート上で移動させ、任意のインピーダンスに変換できることがわかる。

### 3 LNA の設計

#### 3.1 利得

一般に LNA の利得とは  $|S_{21}|$  のことを意味する場合が多い。一般的な  $50\Omega$  系の LNA では、最大有能電力を引き出し大きな利得を実現するためばかりで

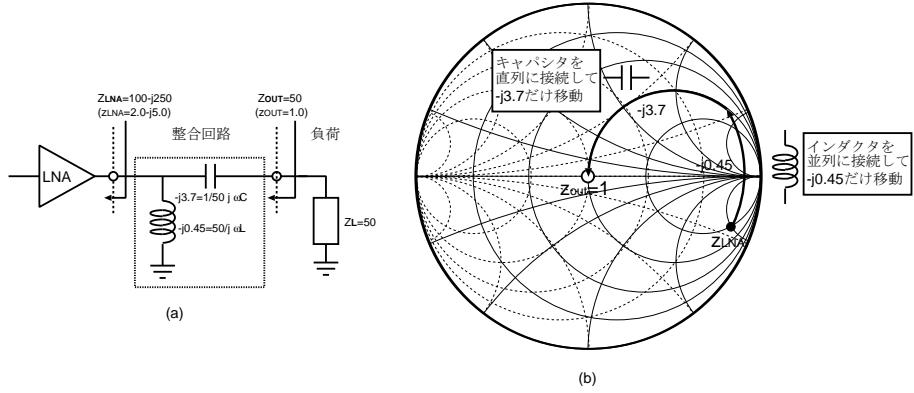

なく、前後に配置されるバンドパスフィルタ (BPF)などを所望の特性で動作させたり、不要な反射を防ぐために、LNA の入力および出力インピーダンスは  $50\Omega$  にインピーダンス整合する。そのために前述のように LNA の入力及び出力には整合回路を用いる。例として図 9 に示すような LNA の出力整合回路を考える。一般にインピーダンス整合を取る前の LNA の出力インピーダンスはキャパシタンス成分を持つため、例えば図 9 に示すように  $Z_{LNA} = 100 - j250$  とする。ここで  $50\Omega$  系である場合を考え、特性インピーダンスの  $50\Omega$  で規格化すると  $z_{LNA} = 2 - j5$  となる。図 9(b) 上で  $Z_{LNA}$  に適当な値のインダクタやキャパシタンスを接続して、チャートの中心に移動させればインピーダンス整合を実現することができる。出力整合回路のトポロジーの組合せは無数に考えられるが、ここでは図 9 に示すように、まずインダクタを並列に付加してアドミタンスチャート上を上に向かって移動し、インピーダンスチャートの中心を通る円周上まで移動させる。このときの移動量をアドミタンス上の目盛で読むと  $j0.45$  となるため、周波数を  $1\text{GHz}$  と仮定すると、接続するインダクタの値は

$$-j \frac{50}{\omega L} = -j0.45 \rightarrow L \sim 17.7[nH] \quad (29)$$

となる。次に、直列にキャパシタを接続し、スミスチャート上を移動し、チャートの中心まで移動する。このときの移動量の目盛をスミスチャートから読み

図 9: LNA の出力整合

図 10: NF の定義

図 12: 定雑音円

取ると  $-j3.7$  であるため、接続するキャパシタの値は

$$-j \frac{1}{50\omega C} = -j3.7 \rightarrow C \sim 860[fF] \quad (30)$$

となる。したがって、図 9 に示すように、LNA の出力に  $17.7\text{nH}$  のインダクタを並列に接続し、さらに  $860\text{fF}$  のキャパシタを直列に接続すると、整合回路を介して見た LNA の出力インピーダンスは  $50\Omega$  となり、負荷の  $50\Omega$  に整合したことになる。このようにスミスチャートを用いると、インピーダンス整合に必要な整合回路のトポロジを決定し、その素子値を計算することができる。

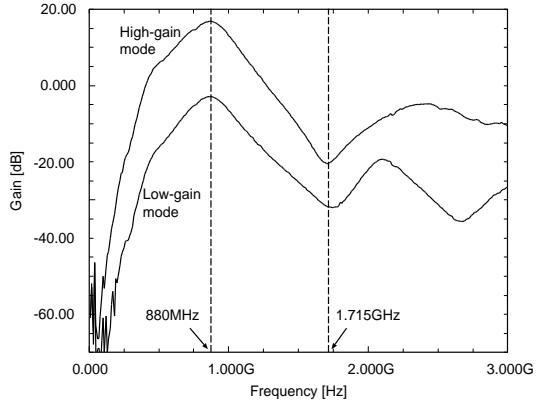

また実際の LNA では、小さな信号が入力した場合に大きな利得と良好な雑音特性で動作する高利得モードと大きな信号が入力した場合に小さな利得と良好な歪特性で動作する低利得モードを切替えて使うことが多い。このような利得切替え機能を LNA に持たせることにより、受信機のダイナミックレンジを大きくすることができる。

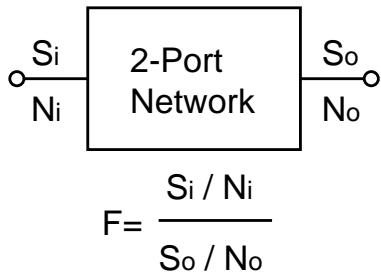

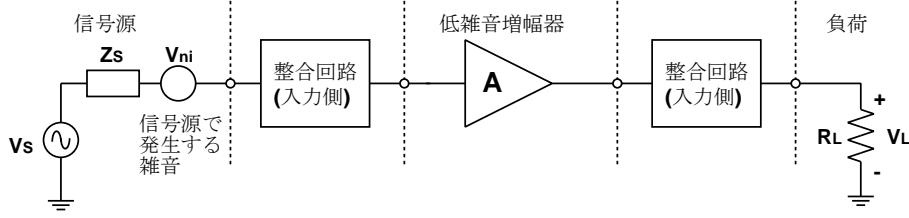

### 3.2 雜音

雑音係数  $F$  は入力の  $S/N$  ( Signal to Noise Ratio ) と出力の  $S/N$  の比で定義され [4]、LNA に入力する雑音 (信号源の熱雑音) と信号の電力をそれぞれを  $N_i$ 、 $S_i$  とし、LNA から出力される雑音と信号の電力をそれぞれ  $N_o$ 、 $S_o$  とし、LNA の利得を  $G$  とすると以下のように書ける。

$$F = \frac{S_i / N_i}{S_o / N_o} = \frac{N_o}{G N_i} = \frac{N_o / G}{N_i} \quad (31)$$

式 (31) より明らかなように、雑音係数  $F$  は LNA から出力される全ての雑音と、信号源で発生する熱雑音の比である。雑音係数  $F$  をデシベルで表示したものが雑音指数 ( $NF$ ) であり

$$NF = 10 \log F [\text{dB}] \quad (32)$$

となる。ここで、信号源で発生する雑音も LNA 内部で発生する雑音も信号源インピーダンス  $Z_S$  によって変化するため、 $F$  および  $NF$  は信号源のインピー-

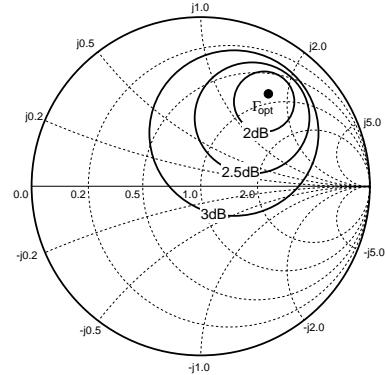

図 11: LNA の NF

ダンス  $Z_S$  によって変化する。実際の信号源インピーダンスのスミスチャート上の位置と  $NF$  の関係は図 12 に示すように、ある一定の  $NF$  となる信号源インピーダンスは同一の円周上に存在する(定雑音円)。この様子は

$$F = F_{min} + \frac{R_n}{G_s} |Y_s - Y_{opt}|^2 \quad (33)$$

のように書け、LNA の雑音特性は雑音係数  $F$  の最小値  $F_{min}$ 、 $F_{min}$  を実現する信号源アドミタンス  $Y_{opt} = G_{opt} + jB_{opt}$ 、 $F$  の変化の勾配を表す  $R_n$  の 4 つのパラメータで規定される [6]。

一般的な LNA では、サイズの大きなトランジスタを用いて、LNA の内部で発生する雑音を小さく抑えるが、大きなサイズのトランジスタを高周波で動作させるためには、大きな消費電流が必要となる。また、LNA の入力側に整合回路を付け、図 12 に示すような  $NF$  が最小になる条件の近傍で使うことが望ましいが、 $NF$  を最小にする入力整合と  $50\Omega$  にインピーダンス整合する条件は同時に成り立たない場合が多い。これらを両立させるため LNA にインダクタでディジエネレーションを施して、 $NF$  を小さくする整合と  $50\Omega$  のインピーダンス整合を両立させるような技術が用いられる [7]。

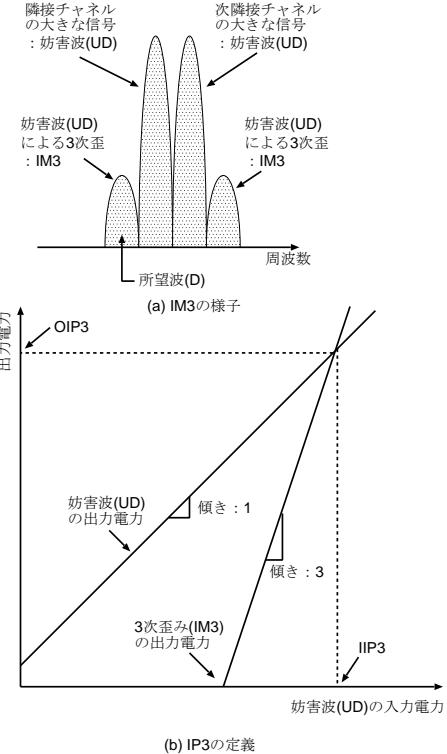

### 3.3 歪

LNA の歪には、大きく分けて弱い非線形の歪を定義する入力換算 3 次インターフェトポイント (IIP3) と強い非線形性を定義する 1dB 利得圧縮点 (P1dB) の 2 つがある。図 13 に IIP3 が想定する状況を示す。LNA の所望波帯域に隣接する 2 本の妨害波 (UD) を入力すると、これらに隣接した周波数に 3 次歪みの成分 (IM3) が現われる [3]。図 13(b) に示すように入力電力をスイープして IM3 を観測し、観測した UD と IM3 に対して直線を外挿し、これらの直線の交点を IIP3 と定義する。

図 13: IIP3 の想定する状況の例

一方、入力電力が大きく、強い非線形性による歪みを規定したのが 1dB ゲインコンプレッションポイントで、ひとつの入力信号を LNA に入力し、入力する電力を大きくしていった場合に、入力信号が十分小さいときに比べ利得が 1dB 小さくなるポイントで定義される。

一般的に LNA の歪みを改善する方法には、抵抗やインダクタでディジエネレーション [4, 7] を行う方法と LNA に供給するバイアス電流を大きくする方法などがあるが、前者はディジエネレーションを行うと利得や雑音特性が劣化するなどの問題が生じ、後者は LNA の消費電力が大きくなるという問題が生じる。

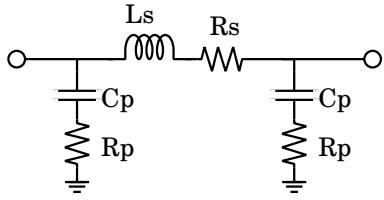

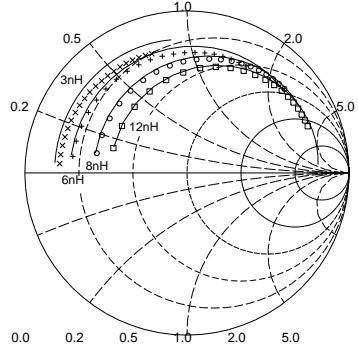

図 14: インダクタの等価回路

図 15: インダクタの実測とシミュレーションの比較

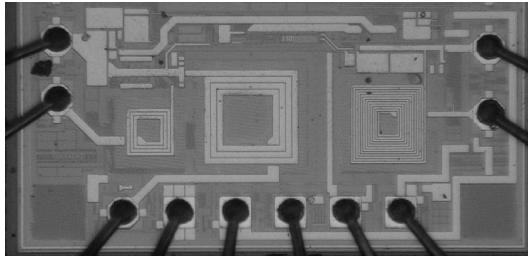

図 17: 800MHz 帯 LNA のチップ写真

## 4 実際の LNA の設計例

### 4.1 高精度なデバイスモデルの重要性

実際に LNA などの高周波回路を設計する場合、高精度なデバイスモデルが重要となってくる [8]-[10]。高精度な回路設計を行うためには、バイポーラトランジスタや MOSFET などの能動素子はもちろん、インダクタ、キャパシタ、抵抗などの受動素子、パッドやパッケージや ESD 保護素子、配線等の寄生素子に至るまで、回路で用いる全ての素子に関して、十分な精度のデバイスモデルを準備する必要がある。例えばスパイラルインダクタの場合、図 14 に示すような等価回路と適切なモデルパラメータを用いることによって、図 15 のように実際のインダクタに近い特性を再現することができる [8]-[9]。

図 18: 800MHz 帯 LNA の利得

### 4.2 携帯電話用の LNA

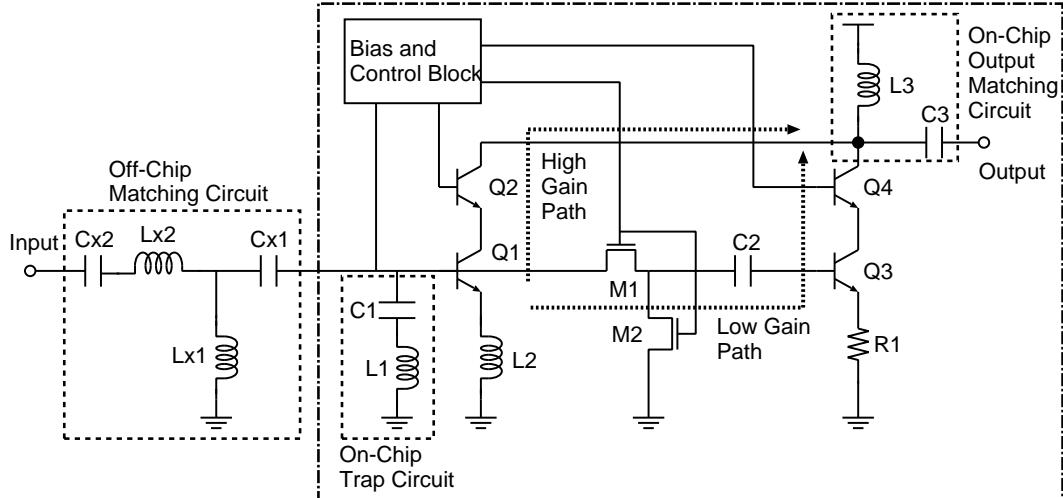

SiGe-BiCMOS プロセスを用いて試作した 800MHz 帯の LNA の回路図を図 16 にチップ写真を図 17 に示す [11, 12]。LNA のオンチップ出力整合回路は、前述した S パラメータやスマスチャートを用いて、 $50\Omega$  に整合するように設計されているが、整合回路に用いているオンチップのインダクタやキャパシタは高周波特性を十分な精度で再現するモデルを用いている。また、図 16 では省略してあるが、パッドや ESD 保護素子、高周波特性に影響するような配線に関しても同様の高周波設計用に抽出したモデルを用いている。さらに実際の設計では、パッケージや評価基板の影響、外付け部品の高周波性能も考慮している。

また、この LNA の入力側には歪を改善するために、オンチップのトラップ回路を集積化し、外付け部品を用いた整合回路は、インピーダンス整合と雑音整合を両立させつつ、歪を低減するように設計してある。さらに、利得切替え機能を実現するために、高利得を持つ経路と低い利得を持つ経路を並列に接続し、各々を切替えて使う構成とした。

図 18 にパッケージに実装して評価した本 LNA の利得を示す。前述した利得切替え機能により、利得が切り替わっていることがわかる。

### 4.3 ミリ波帯の LNA

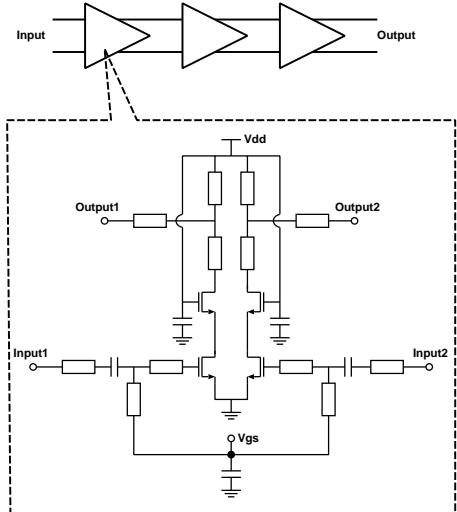

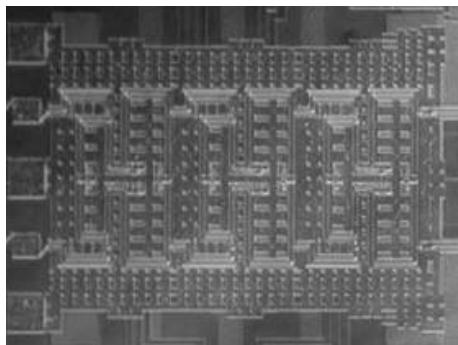

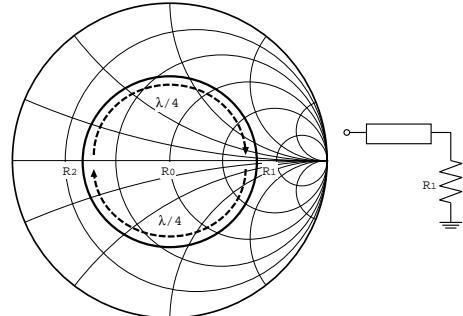

90nm-CMOS プロセスを用いて試作した 60GHz 帯の LNA の回路図を図 19 に、チップ写真を図 20 に示す [13]。数 GHz 帯の LNA ではインダクタとキャパシタを使って整合回路を構成したのに対し、60GHz

図 16: 800MHz 帯 LNA の回路図

帯の LNA では、伝送線路とキャパシタを用いて整合回路を実現している。図 21 に片側を抵抗  $R_1$  で終端した伝送線路の振舞いを示す。ここで  $R_2$  は、終端抵抗  $R_1$  と特性インピーダンス  $R_0$  を用いて

$$R_2 = \frac{R_0^2}{R_1} \quad (34)$$

となる。 $R_1$  で片側を終端した伝送線路は、 $R_1$  および  $R_2$  を通る円周上を半波長毎に一周する。

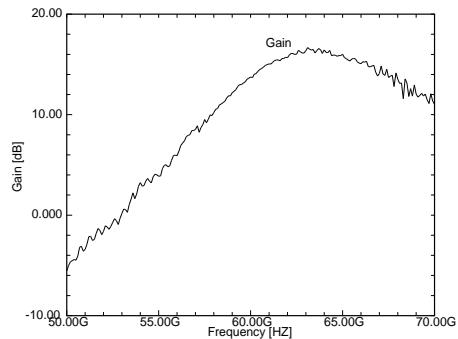

60GHz 帯では増幅器 1 段当たりで得られる利得が低いため、本 LNA では差動のカスコード型の増幅器を 3 段接続にする構成を採用した。各段の増幅器の入出力はいずれも差動  $100\Omega$  に整合されており、段間は特性インピーダンスが  $100\Omega$  の差動の伝送線路で接続されている。

図 22 に本 LNA の利得を、オンウエハで評価した結果を示す。3 段接続の構成にすることで、60GHz という高い周波数においても  $15\text{dB}$  程度の利得を達成している。

## 5 まとめ

本講座では、高性能な高周波回路を実現するためには不可欠な S パラメータやスミスチャートなどの基礎知識と低雑音増幅器 (LNA) を例に高周波回路の設計手法に関して紹介した。本講座で解説した基礎知識と、精度の高いモデルパラメータを用いることにより、Si プロセスでも高性能な高周波回路を実現することができる。

## 参考文献

- [1] 渡部和, "伝送回路網の理論と設計," 第 4 章, オーム社

- [2] 末武国弘, "集中定数回路から分布定数回路へ," 1991 Microwave Workshop and Exhibition (MWE'91), 基礎講座 I, pp.13-44, 1991

- [3] 藤井信生, 関根慶太郎, 高木茂孝, 兵庫明 編 "電子回路ハンドブック," 9.1 章 低雑音増幅器, 朝倉書店, ISBN4254221479

- [4] P. R. Gray and R. G. Meyer, "Analysis and Design of Analog Integrated Circuits," 3rd Edition, Chapter 11, WILEY, New York, 1993

- [5] D.E.Bockelman and W.R.Eisenstadt, "Combined Differential and Common-Mode Scattering Parameters : Theory and Simulation," IEEE Trans. MTT, VOL.43, NO.7, pp.1530-1539, 1995

- [6] 安藤祐二, "マイクロ波デバイスの雑音," MWE'96 Microwave Workshop Digest, T3-1, pp.473-482, 1996

- [7] M.T.Murphy, "Applying the series feedback technique to LNA design," Microwave Journal, pp.143-152, Nov., 1989

- [8] R. Fujimoto, O. Watanabe, F. Fujii, H. Kawakita and H.Tanimoto, "High-frequency

図 19: 800MHz 帯 LNA の回路図

図 20: 60GHz 帯 IC のチップ写真

- device-modeling techniques for RF-CMOS circuits,” IEICE Trans. Fundamentals, Vol.E84-A, No.2, pp.520-528, Feb., 2001

- [9] R. Fujimoto , O. Watanabe, “High frequency device modeling techniques for RF circuits,” MWE 2000 Microwave Workshop Digest, pp.281-286, 2000

- [10] 伊藤信之, “Si デバイス特性と高周波発振回路の基礎,” MWE 2007 Microwave Workshop Digest, 基礎講座 2, 2007

- [11] R. Fujimoto, G. Takemura, M. Ishii, T. Toyoda and H. Tsurumi, “A 900-MHz Low-Noise Amplifier with High Tolerance for Leakage Signal from Transmitter,” International Conference on Solid-State Device and Materials (SSDM 2006), I-6-4L, pp.378-379, Sept., 2006

- [12] R. Fujimoto, G. Takemura, M. Ishii, T. Toyoda and H. Tsurumi, “A Low-Noise Amplifier for WCDMA Terminal with High Tolerance for Leakage Signal from Transmitter,” IEICE Trans. Fundamentals, Vol.E91-A, No.2, Feb., 2008, 採録決定

- [13] T. Mitomo , R. Fujimoto , N. Ono , R. Tachibana , H. Hoshino , Y. Yoshihara, Y. Tsutsumi and I. Seto, “A 60-GHz CMOS Receiver with Frequency Synthesizer,” Tech. Dig. of Symposium on VLSI Circuits, 17-1, pp.172-173, 2007

図 21: 伝送線路の特性

図 22: 60GHz 帯 LNA の利得